| A10PL4 | A10SA4 |

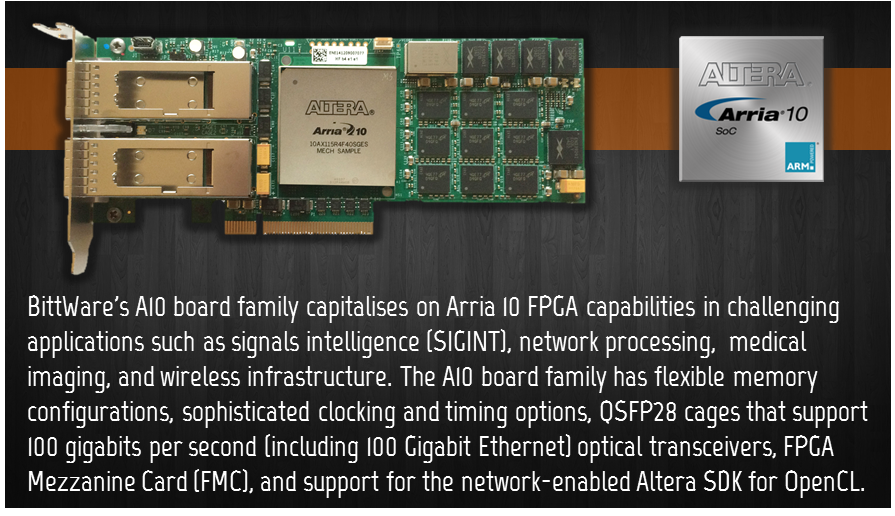

| Intel Arria 10 GT/GX FPGA Low Profile PCIe Board with Dual QSFP and DDR4 |

Arria 10 GX Low Profile PCIe Board with QSFP and DDR4 on BittWare 'Spider' Thermal Platform |

| Datasheet | Datasheet |

BittWare has put two decades of product design experience into creating a mature and robust suite of development tools that is tightly integrated with its FPGA products. These tools for system development and FPGA development shorten our customers’ learning curve while increasing their productivity, allowing them to reduce development costs and shorten their time to market.

| OpenCL Bundle | BittWorks II Toolkit |

| BittWare’s OpenCL Developer’s Bundle provides the tools necessary to begin developing applications for the Altera Arria 10 or Stratix V using OpenCL. Open-CL dramatically simplifies FPGA development by enabling designers to code their systems and algorithms in a high-level C-based framework, directly generating FPGA programming files from a pure software development flow. | The BittWorks II Toolkit is a suite of development tools for BittWare’s FPGA-based hardware that serves as the main interface between the BittWare board and the host system. The Toolkit includes drivers, libraries, utilities, and example projects for accessing, integrating, and developing applications for the BittWare board. |

- OpenCL BSP for Quartus 17.1.1 is now available for the A10PL4 and A10SA4. An updated Hello World example is also available for each board.

- Version 2018.1 of the BittWorks II Toolkit is now available. This is the first toolkit release of 2018. Software releases are numbered as the N'th release of the year. Software releases do not align with FPGA development environment software releases. This is a minor release. We recommend that you upgrade if you are using the Ubuntu operating system.

- Release highlights:

- Support for 4.10 kernel added for Ubuntu 16.04

- Fixed Ubuntu toolkit services

- Add missing BwShell functions

Please contact Sarsen Technology for more information.